| Form PTO-1595 (Rev. 09/04) 09 - U3 - ZV<br>OMB No. 0651-0027 (exp. 6/30/2005)                    |                                                                          |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| OMB No. 0651-0027 (exp. 6/30/2005)                                                               | ET ET                                                                    |

| 1036061                                                                                          | 171 ACT-034-1C                                                           |

|                                                                                                  | se record the attached documents or the new address(es) below.           |

| 1. Name of conveying party(ies)/Execution Date(s):                                               | 2. Name and address of receiving party(ies)                              |

| ZiLOG, Inc.                                                                                      | Name: IXYS CH GmbH                                                       |

|                                                                                                  | Internal Address:                                                        |

| Eobruany 17 2010                                                                                 | 3 2010 3                                                                 |

| Execution Date(s) February 17, 2010  Additional name(s) of conveying party(ies) attached? Yes No | Street Address: Mattenstrasse 6                                          |

| 3. Nature of conveyance:                                                                         |                                                                          |

| Assignment Merger                                                                                | City: Bruegg bei Biel                                                    |

| Security Agreement Change of Name                                                                | State:                                                                   |

| Government Interest Assignment                                                                   | Cusitandand                                                              |

| Executive Order 9424, Confirmatory License                                                       | Country: Switzerland Zip: 2555                                           |

| Other                                                                                            | Additional name(s) & address(es) attached? ☐ Yes ✓ No                    |

| · · · · · · · · · · · · · · · · · · ·                                                            | document is being filed together with a new application.                 |

| A. Patent Application No.(s)                                                                     | B. Patent No.(s)                                                         |

|                                                                                                  | see 170 patents listed on 1-page attachment                              |

|                                                                                                  |                                                                          |

| Additional numbers att                                                                           | tached? Yes No                                                           |

| 5. Name and address to whom correspondence concerning document should be mailed:                 | 6. Total number of applications and patents involved:                    |

| Name: Imperium Patent Works LLP                                                                  |                                                                          |

|                                                                                                  | 7. Total fee (37 CFR 1.21(h) & 3.41) \$_6800.00                          |

| Internal Address: <u>Darien K. Wallace</u>                                                       | Authorized to be charged by credit card                                  |

| 01 1 A -1-1                                                                                      | Authorized to be charged to deposit account  Enclosed                    |

| Street Address: P.O. Box 607                                                                     | None required (government interest not affecting title)                  |

| City: Pleasanton                                                                                 | 8. Payment Information                                                   |

| State: <u>CA</u> Zip: 94566                                                                      | a. Credit Card Last 4 Numbers                                            |

| Phone Number: (925) 550-5067                                                                     | Expiration Date                                                          |

| Fax Number:                                                                                      | b. Deposit Account Number 6800.00 0p                                     |

| Email Address: Darien@ImperiumPW.com                                                             | Authorized User Name                                                     |

| 9. Signature:                                                                                    | Allace August 30, 2010                                                   |

| Signature                                                                                        | Date                                                                     |

| <u>Darien K. Wallace</u><br>Name of Person Signing                                               | Total number of pages including cover sheet, attachments, and documents: |

|                                                                                                  | dilddi mismailiaisa, bita accallici. ;                                   |

Documents to be recorded (including cover sheet) should be faxed to (703) 306-5995, or mailed to:

Mail Stop Assignment Recordation Services, Director of the USPTO, P.O.Box 1450, Alexandria, V.A. 22313-1450

# Continuation of Item 4

| 7733250 | 7117720 | C202001         |                    |  |

|---------|---------|-----------------|--------------------|--|

| 7414553 | 7116739 | 6323091         | 5537564            |  |

| 7414333 | 7068197 | 6424384         | 5428561            |  |

| 7768319 | 6839010 | 6574682         | 5338423<br>5579200 |  |

|         |         | 7353327 7768052 |                    |  |

| 7592843 | 6941416 | 7060584         | 5619681            |  |

| 7411427 | 6915414 | 6166606         | 5734854            |  |

| 7551110 | 6674253 | 6300796         | 5592635            |  |

| 7362255 | 7091795 | 6165846         | 5315184            |  |

| 7508038 | 7002415 | 6576405         | 5317187            |  |

| 7586356 | 6636122 | 6018273         | 5240880            |  |

| 7375571 | 6522091 | 5940284         | 5262687            |  |

| 7414554 | 7170239 | 6190973         | 5244831            |  |

| 7631116 | 7768217 | 6163346         | 5442796            |  |

| 7415599 | 6717377 | 7139037         | 5293562            |  |

| 7148672 | 6768440 | 5995164         | 5262991            |  |

| 7176765 | 5949993 | 6009445         | 5319753            |  |

| 7102452 | 5841365 | 6002449         | 5659688            |  |

| 7212042 | 5697061 | 6436195         | 5471588            |  |

| 7444080 | 5335249 | 6156653         | 5317745            |  |

| 7474857 | 7212749 | 5969390         | 5428252            |  |

| 7574544 | 6915083 | 5978127         | 5265038            |  |

| 7260660 | 6317235 | 5960190         | 5428746            |  |

| 7127538 | 7123840 | 5860013         | 5146115            |  |

| 7379831 | 6590682 | 5926648         | 5263166            |  |

| 7085663 | 6449075 | 5786865         | 5345564            |  |

| 6993441 | 7702244 | 6349122         | 5278957            |  |

| 7711269 | 7181144 | 6064707         | 5093633            |  |

| 7509057 | 6281999 | 6099161         | 5109163            |  |

| 7436345 | 7221285 | 5750426         | 5495594            |  |

| 7230562 | 6970993 | 5608258         | 5287464            |  |

| 7362256 | 6643760 | 5999742         | 5363383            |  |

| 7227492 | 6340903 | 5612634         | 5313621            |  |

| 7742552 | 6339368 | 5381453         | 5230058            |  |

| 7346095 | 6255902 | 5748670         | 5222218            |  |

| 6954083 | 6304111 | 5528242         | 5175831            |  |

| 7296170 | 6833876 | 5479125         | 5239237            |  |

| 7296187 | 6359425 | 6072462         | 5187686            |  |

| 7152010 | 6219279 | 5608425         | 5784292            |  |

| 6907374 | 6502181 | 5369377         | 5231590            |  |

| 7574585 | 6564334 | 5498896         | 5625842            |  |

| 6798713 | 6292045 | 5389565         | 5193199            |  |

| 7342984 | 6154086 | 5602537         |                    |  |

| 7340023 | 6529248 | 5495554         |                    |  |

|         |         |                 |                    |  |

# PATENT ASSIGNMENT

This Patent Assignment (the "Assignment") is made and entered into as of February 18, 2010 (the "Effective Date"), by and among ZILOG, INC., a Delaware corporation ("ZiLOG"), ZiLOG's subsidiaries, ZILOG PHILIPPINES, INC., ZILOG ELECTRONIC PHILIPPINES, INC., ZILOG ASIA LTD., ZILOG JAPAN K.K., ZILOG INTERNATIONAL, LTD., ZILOG INTERNATIONAL PTE. LTD., ZILOG UK, LTD., and ZILOG INDIA ELECTRONICS PRIVATE LTD. ("Assignors") and IXYS CH GMBH, a company organized under the laws of Switzerland ("Assignee"). Defined terms not specifically defined herein shall have the meanings ascribed to them in the Agreement and Plan of Merger, by and among ZiLOG, IXYS Corporation, a Delaware corporation ("Parent"), and Zanzibar Acquisition, Inc., dated December 5, 2009 ("Merger Agreement").

WHEREAS, pursuant to the Merger Agreement, Assignors have agreed to assign to Assignee all patents and patent applications owned by Assignors immediately prior to the Pre-Closing IP Transfer (the "Patents");

WHEREAS, to effect the transfer of the Patents as contemplated in the Merger Agreement, Assignors and Assignee desire to enter into this Assignment;

NOW, THEREFORE, in consideration of the mutual promises of the parties, and for good and valuable consideration, the receipt, adequacy and legal sufficiency of which are hereby acknowledged, the parties hereby agree as follows:

- 1. <u>Assignment</u>. Assignors do hereby sell, assign, transfer, convey and deliver to Assignee, all of the right, title, and interest of Assignor in and to the Patents listed in <u>Annex A</u> attached hereto, and to any continuation, continuation-in-part, division, renewal, substitute, reexamination or reissue thereof or any legal equivalent in the United States or a foreign country for the full term or terms for which the same may be granted, including all priority rights under any international conventions and treaties, together with all claims for damages and other remedies by reason of past infringements of the Patents, whether arising prior to or subsequent to the date of this Assignment, along with the right to sue for and collect such damages and other remedies for the use and benefit of Assignee and its successors, assigns and other legal representatives (the "<u>Transferred Patents</u>").

- 2. <u>Termination of Merger Agreement</u>. If the Merger is not consummated on the date hereof, this Assignment shall immediately terminate and be void without further action of any party hereto. In such event, Assignee shall have no ownership interest whatsoever in the Transferred Patents.

- 3. <u>Authorization</u>. Assignors hereby authorize and request the Commissioner of Patents and Trademarks of the United States to issue patents or other evidence or forms of intellectual property protection or applications to Assignee and its successors, assigns and other legal representatives in accordance with the terms of this Assignment.

1

SV\696199.7

- 4. <u>Conflicts</u>. This Assignment is subject to and controlled by the terms of the Merger Agreement, and in the event of any conflict or inconsistency between the terms of the Merger Agreement and the terms hereof, the terms of the Merger Agreement shall govern.

- 5. <u>Further Actions</u>. Each of the parties hereto covenants and agrees, at its own expense, to execute and deliver, at the request of the other party hereto, such further instruments of transfer and assignment and to take such other action as such other party may reasonably request to more effectively consummate the assignments and assumptions contemplated by this Assignment..

- 6. <u>Binding Assignment</u>. Assignors may not, directly or indirectly, in whole or in part, whether voluntarily or involuntarily or by operation of law or otherwise, assign or transfer this Assignment and the rights granted to it hereunder without Assignee's prior written consent, which consent may be granted or refused at Assignee's sole discretion. Any assignment or attempted assignment in violation of this Section shall be null and void from the beginning, and shall be deemed a material breach of this Assignment.

- 7. Relationship Between Parties. Assignee and Assignors shall at all times and for all purposes be deemed to be independent contractors and neither party, nor either party's employees, representatives, subcontractors or agents, shall have the right or power to bind the other party. This Assignment shall not itself create or be deemed to create a joint venture, partnership or similar association between Assignee and Assignors or either party's employees, representatives, subcontractors or agents.

- 8. <u>Counterparts</u>. This Assignment may be executed in two or more counterparts, all of which, taken together, shall be considered to be one and the same instrument. The exchange of a fully executed Assignment (in counterparts or otherwise) by facsimile transmission, by electronic mail in "portable document format" (".pdf") form, or by any other electronic means intended to preserve the original graphic and pictorial appearance of a document, shall be sufficient to bind the parties to the terms and conditions of this Assignment.

- 9. <u>Entire Assignment</u>. With the exception of the Merger Agreement, this Assignment supersedes any arrangements, understandings, promises or agreements made or existing between the parties hereto prior to or simultaneously with this Assignment and, together with the Merger Agreement, constitutes the entire understanding between the parties hereto.

[SIGNATURE PAGE FOLLOWS]

2

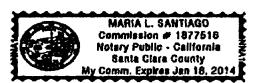

IN WITNESS WHEREOF, Assignee has caused this Assignment to be executed as of the Effective Date. ACKNOWLEDGEMENT: STATE OF CALIFORNIA COUNTY OF SANTA CLAMA) On FEDRULLY 14, 2010 before me Horo T, Lee, personally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is/are subscribed to the within instrument and acknowledged to me that he/she/they executed the same in his/her/their authorized capacity(ies), and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument. I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct. WITNESS my hand and official seal Signature Hoy & Kel (Seal)

Signature Page to Patent Assignment

IN WITNESS WHEREOF, Assignors have caused this Assignment to be executed as of the Effective Date. ZILOG, IN Name: Title: ACKNOWLEDGEMENT: STATE OF CALIFORNIA COUNTY OF Santa Clara; ss:

17,2010 before me Maria L. Santiacopersonally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is are subscribed to the within instrument and acknowledged to me that he she/they executed the same in his/her/their authorized capacity(ies). and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal

(Seal)

Signature Page to Patent Assignment

| ZiLOG  | Punge  | PINES, I | NC.   |

|--------|--------|----------|-------|

| Ву:    | ( Jany | 9/       |       |

| Name:  | PER    | 级头       | GRACE |

| Title: | Die    | Ecolo    |       |

STATE OF CALIFORNIA

SS:

COUNTY OF Santa Clave

on the basis of satisfactory who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) are subscribed to the within instrument and acknowledged to me that he she/they executed the same in his her/their authorized capacity (ies), and that by his her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

Signature 1

(Seal)

Signature Page to Patent Assignment

PATENT

REEL: 024964 FRAME: 0138

| ZILOG ELECTRONIC PHILIPPINES, INC. |                |  |

|------------------------------------|----------------|--|

| Ву:                                |                |  |

| Name:                              | PERRY I GRACE. |  |

| Title:                             | DIRECTOR       |  |

|                                    |                |  |

STATE OF CALIFORNIA

COUNTY OF Santa clara, ss:

on Feb 17, 2010 before mellow a L. Sant and personally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is are subscribed to the within instrument and acknowledged to me that he/she/they executed the same inhig/her/their authorized capacity(ies), and that by his her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal. · Doublage

(Seal)

Signature Page to Patent Assignment

| ZILOG  | ASIALT | D.    |   |       |   |

|--------|--------|-------|---|-------|---|

| Ву:    | ( Jen  | 1/2   |   |       | _ |

| Name:_ | PEN    | RY    | I | GRACE |   |

| Ti+las | Die    | 64870 | ) | •     | _ |

STATE OF CALIFORNIA

SS:

COUNTY OF SOLLA CLOVA

On Feb 17 2010 before me 1000 L. Sand-copersonally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is are subscribed to the within instrument and acknowledged to me that he she/they executed the same in his/her/their authorized capacity(ies), and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

Signature Maria L. Louteau

(Seal)

Signature Page to Patent Assignment

| ZILOC   | Inpernational, Ltd. |

|---------|---------------------|

| Ву:     | (Jang 1)            |

| Name:   | PENRY J GRACE       |

| Title:_ | DIRECTOR            |

COUNTY OF Santa Clara; ss

On FeV 17, 2010 before me WOLL. Sath appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is are subscribed to the within instrument and acknowledged to me that has help executed the same in his her/their authorized capacity (ies), and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

Signature

(Seal)

Signature Page to Patent Assignment

| ZiLOG  | NERNATIONAL PTE. LTD. |

|--------|-----------------------|

| By:(   | lang/ 5               |

| Name:  | REPRENT GRACE         |

| Title: | DIRECTOR.             |

STATE OF CALIFORNIA

SS:

COUNTY OF Santa clara

on to local before me May a local personally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) are subscribed to the within instrument and acknowledged to me that he/she/they executed the same inhis/her/their authorized capacity(ies), and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

Signature

(Seal)

Signature Page to Patent Assignment

| ZiLOG  | UK LTD.        |

|--------|----------------|

| Ву:    | ( semples      |

| Name:  | Person J BRACE |

| Title: | DIRECTUAL      |

STATE OF CALIFORNIA

SS

COUNTY OF Santa clasa

before me \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \( \) \(

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

Signature / W. A.

(Seal)

Signature Page to Patent Assignment

ZILOG INDIA ELECTRONICS PRIVATE LTD. By: Name: Title: before md NOCOL Sant Qoo personally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) is are subscribed to the within instrument and acknowledged to me that he she they executed the same in his her/their authorized capacity(ies), and that by his/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument. I certify under PENALTY OF PERJURY under the laws of the State of California that the

foregoing paragraph is true and correct. WITNESS my hand and official seal.

ACKNOWLEDGEMENT:

STATE OF CALIFORNIA

COUNTY OF Santa clara

(Seal)

Signature Page to Patent Assignment

| ZiLOGJ | APAN K.K. |         |

|--------|-----------|---------|

| Ву:(   | my 19     |         |

| Name:  | PERRY     | J GRACE |

| Title: | DIRECT    | DR-     |

STATE OF CALIFORNIA

county of Santa Clara

On FeV 17. 7010 before me Maria L. Santago personally appeared who proved to me on the basis of satisfactory evidence to be the person(s) whose name(s) sare subscribed to the within instrument and acknowledged to me that he she/they executed the same inhis/her/their authorized capacity(ies), and that by (ii)/her/their signature(s) on the instrument the person(s), or the entity upon behalf of which the person(s) acted, executed the instrument.

I certify under PENALTY OF PERJURY under the laws of the State of California that the foregoing paragraph is true and correct.

WITNESS my hand and official seal.

(Seal)

Signature Page to Patent Assignment

### ANNEX A

#### **Transferred Patents**

# **Patents**

US7123840 Infrared Signal Communication System and Method Including Transmission Means Having Automatic Gain Control

US7414553 Microcontroller Having In-Situ Autocalibrated Integrating Analog-To-Digital Converter (IADC)

US7460966 Low Current Analog Circuit

US7592843 Clock Input Filter Circuit

US7411427 RC Based Clock Noise Filter Circuit

US7551110 Chopping and Oversampling ADC Having Reduced Low Frequency Drift

US7362255 Chopping and Oversampling ADC Having Reduced Low Frequency Drift

US7508038 A Novel Grounded Gate NMOS ESD Protection Transistor

US7586356 Glitch Free Clock Multiplexer that Uses a Delay Element to Detect a Transition-Free Period in a Clock

US7375571 Glitch Free Clock Multiplexer that Uses a Delay Element to Detect a Transition-Free Period in a Clock

US7414554 Linearity Correction for Analog to Digital Converters

US7415599 Operation and Operand Inference for Extended-Precision Computation

US7148672 Low Voltage Bandgap Reference Circuit with Startup Control

US7176765 Internal Precision Oscillator with master current source to control switching thresholds

US7102452 Internal Precision Oscillator with master current source to control switching thresholds

US7212042 Below Ground Sensing Amplifier

US7444080 IrDA Transmitter Circuit Having Low Energy Consumption

US7474857 RECOVERING ENERGY FROM AN IRDA/REMOTE CONTROL TRANSMITTER CIRCUIT

US7574544 Flow Control By Supplying A Remote Start Bit Onto A Single-Wire Bus

US7260660 Flow Control by Supplying a Remote Start Bit Onto a Single-Wire Bus

US7127538 Single-Pin Serial Communication Link wiht Start-Bit Flow Control

US7379831 Error Correction in an Oversampled ADC Using Few Stored Calibration Coefficeents

US7085663 Adaptive Error Correction in an Oversampled ADC

SV\696199.7

US6993441 Adaptive Error Correction in an Oversampled ADC

US7509057 IRDA Transceiver Module That Also Functions as Remote Control IR Transmitter

US7436345 A Script Instruction For Jumping To A Location, Interpreting A Predetermined Number of Instructions

US7230562 Sending A Script to a Virtual Machine for Immediate Interpreting

US7362256 Loading A Machine Code API Onto An 8-Bit Virtual Machine to Enable New Functionality

US7227492 Interpreting A Common Script Block to Output Various Forms of Data To A Common Protocol

US7346095 Spread Spectrum Clock Generator With Controlled Delay Elements

US6954083 Circuit for Detection of Hardware Faults Due to Temporary Power Supply Fluctuations

US7296170 Clock Controller with Clock Source Fail-Safe Logic

US7296187 Hardware Debug Device Having Script-Base Host Interface

US7152010 Calibrating an Analog to Digital Converter Using a Test Signal With Precise DC Voltage

US6907374 Method and Apparatus for Correction of Sigma-Delta ADC Accuracy Errors

US7574585 Implementing Software Breakpoints and Debugger Therefor

**US6798713** Implementing Software Breakpoints

US7342984 Counting Clock Cycles Over the Duration of a First Character and Using a Remainder Value to Determin

US7340023 Auto Baud System and Method and Single Pin Communication Interface

US7116739 Auto Baud System and Method and Single Pin Communication Interface

US7106209 Programming A Universal Remote Control

US7068197 ADC With Reduced Quantization Noise and Programmable Bit Resolution

US6839010 Improvement of Amplitude Resolution of Sigma-Delta Analog-to-Digital Converter with Adaptive Filter

US7353327 Dedicated Command Port in Memory Controllers

US6941416 Apparatus and Methods for Dedicated Command Port in Memory Controllers

US6915414 Context Switching Pipelined Microprocessor

US6674253 Scan Velocity Modulation Technique

US7091795 Modulating Ramp Angle in a Digital Frequency Locked Loop

US7002415 Modulating Ramp Angle in a Digital Frequency Locked Loop

SV\696199.7

US6636122 Analog Frequency Locked Loop with Digital Oversampling Feedback Control and Filter

US6522091 Circuit and Method That Allows the Amplitudes of Vertical Correction Signal Components to be Adjusted

US7,170,239 B2 Circuit and Method for Reducing East-West Geometry Mismatch Between the Top and Bottom of a Raster Display

US6717377 Circuit and Method for Reducing East-West Geometry Mismatch Between the Top and Bottom of a Raster Display

US6849510 Non-Oxidizing Spacer Densification Method for Manufacturing Semiconductor Devices

US6642112 Non-Oxidizing Spacer Densification Method for Manufacturing Semiconductor Devices

US6768440 Digital-to-Analog Converters with Reduced Parasitics and Associated Methods

EP(UK)1025492 Method for the Generation of ISA Simulators and Assemblers from a Machine Language

US5949993 Method for the Generation of ISA Simulators and Assemblers from a Machine Language

US5841365 Method and Apparatus for Communicating with a Product Label

US5697061 Method and Apparatus for Providing Information Concerning Products, Using Radio Frequency Transmission

US5335249 Method and Apparatus for Spread Spectrum Communications

US7212749 Signal Receiver Having Wide Band Amplification Capability

US6317235 Method and System for Preventing Burn-Out of Infrared Transmitter Diodes

US7221285 Improved Standby Mode for Infrared Data Transceivers

US6590682 Improved Infrared Signal Communication System and Method Including Transmission Means Having Automatic Gain Control

US6449075 Method and System for Enabling Wireless Data Communications with Electronic Devices Having Disparate Operating Systems

US7181144 Circuit Design and Optics System for Infrared Signal Transceivers

US6281999 Improved Optics System for Infrared Signal Transceivers

US6,970,993 B2 Architecture to Relax Memory Performance Requirements

US6643760 Architecture to Relax Memory Performance Requirements

US7042366 Use of Remote Controls for Audio-Video Equipment to Control Other Devices

US6340903 Auto-Zero Feedback Sample-Hold System

SV\696199.7

US6339368 Circuit for Automatically Having Mechanical Device at Its Resonance Frequency

US6255902 Switch Amplifier Circuit

US6304111 CMOS Switch Circuit Having Concurrently Switching Complementary Outputs Independent From Process Variations

US6833876 Using a Reduced Memory Lookup Table for Gamma Correction Through Interpolation

US6359425 Current Regulator with Low Voltage Detection Capability

US6219279 Non-Volatile Memory Program Driver and Read Reference Circuits

US6502181 Method and Apparatus for an Enhanced Processor

US6564334 Memory Mapped Programmable Generator Ouputting Series of Events with Timing Derived from Event Block

US6292045 Circuit and Method for Detecting and Selecting Clock Sources

US6154086 Low Ripple Power Distribution System

US6529248 Method and Apparatus for Improved Signal Restoration

US6323091 Method of Forming Semiconductor Memory Device with LDD

US6424384 Method and Apparatus for Improved Signal Filtering

US6574682 Data Flow Enhancement for Processor Architectures with Cache

US7060584 Process to Improve High Performance Capacitor Properties in Integrated MOS Technology

US6166606 Phase and Frequency Locked Clock Generator

US6300796 High Voltage PMOS Level Shifter

US6165846 Method of Eliminating Gate Leakage in Nitrogen Annealed Oxides

US6576405 High Aspect Ratio Photolithographic Method for High Energy Implantation

US6407779 Method and Apparatus for an Intuitive Universal Remote Control System

US6018273 Externally Synchronized Voltage Controlled Oscillator in Phase Locked Loop

US5940284 Low Voltage Charge Pump Circuit

US6190973 Method of Fabricating a High Quality Thin Oxide

US6163346 Dot Crawl Reduction in NTSC/PAL Graphic Encoder

US7139037 Circle Correction in Digital Low-Pass Filter

US5995164 Reduction of Color Transition Distortions in NTSC/PAL Encoder

US6009445 Reconfigurable Infinite Impulse Response Digital Filter

EP1023804 Integrated Television Processor

SV\696199.7

| US6002449 Integrated Television Processor                                                                       |

|-----------------------------------------------------------------------------------------------------------------|

| US6436195 Method of Fabricating a MOS Device                                                                    |

| US6156653 Method of Fabricating a MOS Device                                                                    |

| US5969390 Layout Solution for Electromagnetic Interference Reduction                                            |

| US5978127 Light Phase Grating Device                                                                            |

| US5960190 In-Circuit Emulation System with Minimal Impact on Target Environment                                 |

| TW98783 Flexible Interrupt System for an Integrated Circuit                                                     |

| US5860013 Flexible Interrupt System for an Integrated Circuit                                                   |

| US5926648 I/O Port and RAM Memory Addressing Technique                                                          |

| US5786865 Apparatus and Method for Digital Amplitude and Phase Detection                                        |

| US6349122 Apparatus and Method for Data Synchronizing and Tracking                                              |

| US6064707 Apparatus and Method for Data Synchronizing and Tracking                                              |

| US6099161 Asynchronous Analog or Digital Frequency Measurement on Digital Test Equipment                        |

| US5750426 MOS Precision Capacitor with Low Voltage Coefficient                                                  |

| US5608258 MOS Precision Capacitor with Low Voltage Coefficient                                                  |

| US5999742 Dual Latch Data Transfer Pacing Logic Using a Timer to Maintain a Data Transfer Interval              |

| US5612634 Circuit for Sensing Whether or not an Add-In Board is Inserted into a Bus Connector of a Mother Board |

| US5640137 Polysilicon Resistor Cooling                                                                          |

| US5381453 Efficient Functional Test Scheme Incorporated in a Programmable Duration Binary Counter               |

| US5748670 Method of Demodulating Chirp Spread Spectrum                                                          |

| US5528242 Flash Analog-to-Digital Converter                                                                     |

| US5479125 Frequency Multiplying Clock Signal Generator                                                          |

|                                                                                                                 |

US6072462 Technique for Generating On-Screen Display Characters Using Software Implementation

US5608425 Technique for Generating On-Screen Display Characters Using Software Implementation

US5369377 Circuit for Automatically Detecting Off-Chip, Crystal or On-Chip, RC Oscillator Option

US5498896 High Threshold Metal Oxide Silicon Read-Only-Memory Transistors

US5389565 Method of Fabricating High Threshold Metal Oxide Silicon Read-Only-Memory Transistors

SV\696199.7

US5602537 Technique for Eliminating Transmit Memory Underruns

US5495554 Analog Wavelet Transform Circuitry

US5537564 Technique for Accessing and Refreshing Memory Locations Within Electronic Storage Devices

US5428561 Efficient Pseudorandom Value Generator

US5338423 Method of Eliminating Metal Voiding in a Titanium Nitride/Aluminum Processing

US5579200 Electrostatic Discharge Protection for Metal-Oxide-Silicon Feedback Elements Between Pins

US5619681 Delayed FIFO Status for Serial Shift Emulation

JP3547740 Fast Instruction Decoding in a Pipeline Processor

US5734854 Fast Instruction Decoding in a Pipeline Processor

US5592635 Technique for Accelerating Instruction Decoding of Instruction Sets with Variable Length Opcodes

US5315184 Self Arbitrating Auto Resettable Flag Circuit

**US5317187 Contact Metallization**

US5240880 Contact Metallization

US5262687 Decoder Circuit with Bypass Circuitry and Reduced Input Capacitance for Greater Speed

US5244831 Method of Doping a Polysilicon Layer on a Semiconductor Wafer

US5442796 Pulse Generator and Demodulator with Controlling Processor and Decrementing Counters

US5293562 Device with Multiplexed and Non-Multiplexed Address and Data I/O Capability

US5262991 Device with Multiplexed and Non-Multiplexed Address and Data I/O Capability

US5319753 Qeued Interrupt Mechanism with Supplementary Command/Status/Message Information

US5659688 Technique and Circuit for Providing Two or More Processors with Time Multiplexed Access to a Shared Resource

US5471588 Technique and Circuit for Providing Two or More Processors with Time Multiplexed Access to a Shared Resource

US5317745 Minimal Interrupt Latency Scheme Using Multiple Program Counters

US5428252 Power Supply Interruption Detection and Response System for a Microcontroller

SV\696199.7

US5265038 Computer System Peripheral Connection Pulse Filtering Technique and Circuit

US5428746 Integrated Microprocessor Unit Generating Separate Memory and Input-Output Device Control Signals

US5146115 Domino-Logic Decoder

US5263166 Technique of Programming Integrated Circuit Control Registers

US5345564 Serial Communication Peripheral Integrated Electronic Circuit That Recognizes Its Unique Address

US5278957 Data Transfer Circuit for Interfacing Two Bus Systems That Operate Asynchronously with Respect to Each Other

US5093633 Externally Trimmed Integrated-Circuit RC Oscillator

US5109163 Integrated Power-On Reset Circuit

US5495594 Technique for Automatically Adapting a Peripheral Integrated Circuit for Operation with a Variety

US5287464 Semiconductor Multi-Device System with Logic Means for Controlling the Operational Mode

US5363383 Circuit for Generating a Mode Control Signal

US5313621 Programmable Wait States Generator for a Microprocessor and Computer System Utilizing It

US5230058 IC Chip Having Volatile Memory Cells Simultaneously Loaded with Initialization Data

US5446742 Techniques for Developing Integrated Circuit Test Programs and Their Use in Testing Actual Circuits

US5028819 High Voltage CMOS Open-Drain Output Buffer

US5222218 System with Devices Connected in Sequence to Receive Information in a Predetermined Order

US5175831 System Register Initialization Technique Employing a Non-Volatile/Read Only Memory

US5239237 Control Circuit Having Outputs with Differing Rise and Fall Times

US5187686 Control Circuit Having Outputs with Differing Rise and Fall Times

KR168829 Technique for Merging Two or More Individual Integrated Circuits

JP3244270 Technique for Merging Two or More Individual Integrated Circuits into a Single Integrated Circuit

US5784292 Merging Integrated Circuit Mask Databases Formed By Different Design Rules Through Global Mask Database

US5231590 Technique for Modifying an Integrated Circuit Layout

SV\696199.7

KR169302 Color Display Control Circuit for CRT

US5373308 Color Bargraph Display Control for Use with a Cathode Ray Tube

US5625842 System for the Automatic Transfer of Message Status in Digital Data Communication

US5193199 Device and Method for Programming Critical Hardware Parameters

US 7,629,828 Glitch-free clock multiplexer that provides an output clock signal based on edge detection

## Patent Applications

N/A Network Master for Wireless Flourscent Lamp Lighting Control Networks filed in US on: October 30, 2009

N/A Time-Hopping Low-Power Wireless Network for Turning Off and On Flourescent Lamps filed in US on: September 30, 2009

12/587,062 Low-Power Wireless Network Beacon for Turning Off and On Flourescent Lamps filed in US

12/587,169 Dimming a Multi-Lamp Flourescent Light Fixture by Turning Off An Individual Lamp Using a Wireless Flourescent Lamp Starter filed in US

12/587,130 Turning Off Multiple Fluorescent Lamps Simultaneously using RF-enabled Lamp Starter Units filed in US

12/587,152 Registering a Replaceable RF-Enabled Flourescent Lamp Starter Unit to a Master Unit filed in US

PCT/US09/002240 Process and System of Energy Signal Detection filed in PCT US10/082472

12/383,167 Receiving an IR Control Signal Through a Fresnel Lens of a Motion Sensor filed in US

12/291,574 Power monitor (50hz & 60hz) omnibus filed in US

12/286,562 Pulsed clock inputs to improve false lock rejection in DLL filed in US

12/315,169 Automatic storage and retrieval of favorite channel filed in US

12/319, 775 Dynamic Shared Dual Bus Controller filed in US

12/229,574 A method to prevent semiconductor SRAM memory from retaining residual information after power is removed filed in US

12/154,611 Low Cost and Noise Insensitive Motion Detector filed in US

12/221,161 Low-Cost Magnetic Stripe Reader Using Independent Switching Thresholds filed in US

12/214,479 Press-Fit Integrated Circuit Package Involving Compressed Spring Contact Beams filed in US

11/904,749 General Purpose Ball Grid Array Security Cap filed in US

SV\696199.7

12/386,590 Glitch Free Clock Multiplexer That Provides An Output Signal Based on Edge Detection filed in US

11/796,644 Glitch Free Clock Multiplexer That Provides An Output Signal Based on Edge Detection filed in US

11/644,499 Internal Voltage Trimming for Bandgap Circuit for Test-time Reduction filed in US

11/701,137 Frequency Trimming for Internal Oscillator for Test-time Reduction filed in US

12/228,824 Mircocontroller Having In-Situ Autocalibrated Integrating Analog to Digital Converter (IADC) filed in US

11/479,037 Open-Loop Transimpedance Amplifier for Infrared Diodes filed in US

11/345,803 Blank Bit and Processor Instructions Employing the Blank Bit

11/339,233 Accelerometer based PC mouse filed in US

11/271,453 Vectored Back to Back Interrupts filed in US

12/584,803 Clock Input Filter Circuit filed in US

12/383,534 A Novel Grounded Gate NMOS ESD Protection Transistor filed in US

12/228,223 Operation and Operand Inference for Extended-Precision Computation filed in US

11/495,913 Sample and Hold Time Stamp for Sensing Back EMF Zero Crossing In 3 Phase Brushless DC motors filed in US

11/448,514 Latent VBO (Voltage Brown Out) Reset Circuit filed in US

11/437,884 Controlling Transmission Power in an IrDA/RC Transmitter Circuit filed in US

12/315,214 RECOVERING ENERGY FROM AN IRDA/REMOTE CONTROL TRANSMITTER CIRCUIT filed in US

12/383,510 IRDA Transceiver Module That Also Functions as Remote Control IR Transmitter filed in US

60/576,941 A Compact Register-Based Virtual Machine and its use on Resource Constrained Devices, filed in US

12/319,704 Loading a machine code API onto an 8-bit virtual machine to enable new functionality filed in US

12/077,282 Spread Spectrum Clock Generator With Controlled Delay Elements filed in US

10/820,237 Circuit and Method for Reducing East-West Geometry Mismatch Between the Top and Bottom of a Raster Display filed in US

09/654,858 METHOD AND SYSTEM FOR ELECTRONIC DATA SALES AND DISTRIBUTION OVER WIDE AREA COMPUTER NETWORKS filed in US

SV\696199.7

11/289,262 Process to Improve High Performance Capacitor Properties in Integrated MOS Technology filed in US

US7339513 Interpreting a script to generate an operational signal on a remote control device

US application 12/148,925

US7286076 Generating a mark/space table and a string of timing information on a remote control device

US application 12/319704

US application 10/928808

SV\696199.7

**RECORDED: 09/03/2010**