## PATENT ASSIGNMENT

## Electronic Version v1.1 Stylesheet Version v1.1

SUBMISSION TYPE: NEW ASSIGNMENT

NATURE OF CONVEYANCE: ASSIGNMENT

#### **CONVEYING PARTY DATA**

| Name          | Execution Date |

|---------------|----------------|

| MetaRAM, Inc. | 09/11/2009     |

#### RECEIVING PARTY DATA

| Name:           | Google Inc.               |

|-----------------|---------------------------|

| Street Address: | 1600 Amphitheatre Parkway |

| City:           | Mountain View             |

| State/Country:  | CALIFORNIA                |

| Postal Code:    | 94043                     |

#### PROPERTY NUMBERS Total: 1

| Property Type       | Number   |

|---------------------|----------|

| Application Number: | 13181747 |

#### CORRESPONDENCE DATA

Fax Number: (877)769-7945 Email: apsi@fr.com

Correspondence will be sent to the e-mail address first; if that is unsuccessful, it will be sent via US

Mail

Correspondent Name: Joseph Valentino

Address Line 1: FISH & RICHARDSON P.C.

Address Line 2: P.O.BOX 1022

Address Line 4: MINNEAPOLIS, MINNESOTA 55440-1022

ATTORNEY DOCKET NUMBER: 16113-1929011

NAME OF SUBMITTER: Roselynn Scarfo

## Total Attachments: 6

source=MetaRAMtoGoogleAssignment1929#page1.tif

source=MetaRAMtoGoogleAssignment1929#page2.tif

source=MetaRAMtoGoogleAssignment1929#page3.tif

source=MetaRAMtoGoogleAssignment1929#page4.tif

source=MetaRAMtoGoogleAssignment1929#page5.tif

source=MetaRAMtoGoogleAssignment1929#page6.tif

PATENT REEL: 026977 FRAME: 0903 CH \$40,00 1318

501672143

## © IN THE UNITED STATES ATENT AND TRADEMARK OFFICE

#### PATENT ASSIGNMENT

WHEREAS, MetaRAM, Inc., hereinafter referred to as "Assignor," a Delaware corporation with a place of business at 101 Metro Drive, Suite 350, San Jose CA 95110 is the sole owner of the entire right, title and interest in and to the patents and patent applications listed in Exhibit A to this Assignment (collectively, "Listed Patents and Applications"); and

WHEREAS, Google Inc., hereinafter referred to as "Assignee," a Delaware corporation with a place of business at 1600 Amphitheatre Parkway, Mountain View, CA 94043, is desirous of obtaining the entire right, title and interest in and to the Listed Patents and Applications;

NOW, THEREFORE, in consideration of good and valuable consideration, the receipt of which is hereby acknowledged, Assignor has sold, assigned, transferred and set over, and by these presents does hereby sell, assign, transfer and set over, unto said Assignee, its successors, legal representatives and assigns, its entire right, title and interest in, to and under the said the Listed Patents and Applications, including all pending applications, as well as all divisions, renewals and continuations thereof, and all Letters Patent of the United States which may be granted thereon and all reissues and extensions thereof, and all applications for Letters Patent which may hereafter be filed for inventions embodied by said pending applications in any country or countries foreign to the United States, and all Letters Patent which may be granted for said inventions embodied by said pending applications in any country or countries foreign to the United States and all extensions, renewals and reissues thereof and all rights of priority in any such country or countries based upon the filing of said pending applications in the United States which are created by any law, treaty or international convention; and I hereby authorize and request the Commissioner of Patents of the United States, and any Official of any country or countries foreign to the United States, whose duty it is to issue patents on any such applications as aforesaid, to issue all Letters Patent for said inventions to Google Inc., its successors, legal representatives and assigns, in accordance with the terms of this instrument.

MetaRAM. Inc.

Name: SURECH RAJAN

Title: PRESIDENT & CEO

PATENT

REEL: 026977 FRAME: 0904

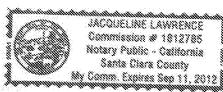

STATE OF COUNTY OF Santa Clara On this 11th day of Score we personally appeared Surgh Kalan personally known to me (or proved on the basis of satisfactory evidence) to be the person whose name is subscribed to this Assignment, who, being duly sworn, did say that he is the President and CEO of MetaRAM, Inc., and that he duly executed the foregoing instrument for and on behalf of MetaRAM, Inc., being duly authorized to do so and that said individual acknowledged said instrument to be the free act and deed of said corporation. My commission expires: Sep. 11, 2012 On SEPTIME WE LAN, before me, 7244 N. 6745, AND PAGE personally appeared SOVACO & MARCH SOV. Who proved to me on the basis of satisfactory evidence to be the person whose name is subscribed to this Assignment and acknowledged to me that he executed the same in his authorized capacity, and that by his signature on this Assignment the person(s); or the entity upon behalf of which the person(s) acted, executed this Assignment. I certify under PENALTY OF PERJURY under the laws of the State of California that

WITNESS my hand and official seal.

the foregoing paragraph is true and correct.

MARIANO CURAT

Commission # 1851849

Notary Public - California

San Francisco County

My Comm. Expires Jun 28, 2013

Notary-Public

# Exhibit A

| MRAM<br>ID | ED.                    | Title                                                                                                                                                   | Jurisdiction |

|------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 0001       | 60/693631              | An Integrated Memory Core And Memory                                                                                                                    | US           |

|            |                        | Interface Circuit                                                                                                                                       |              |

| 0001       | PCT/US2007002324       | An integrated Memory Core and Memory<br>Interface Circuit                                                                                               | WO           |

| 0001       | 7515453                | An Integrated Memory Core And Memory Interface Circuit                                                                                                  | US           |

| 0002       | 60/713815              | Methods And Apparatus of Stacking DRAMs                                                                                                                 | US           |

| 0003       | 60/772414              | Multi-Rank Memory Buffer and Memory Stack                                                                                                               | US           |

| 0005       | 60/814234              | Memory Systems and Memory Modules                                                                                                                       | US           |

| 0006       | 11/515167              | Stackable Low-Profile Lead Frame Package                                                                                                                | US           |

| 0007       | 11/588739              | Active Raw Card For Dual In Line Memory Module                                                                                                          | 85           |

| 0009       | US20070014168          | Method and Circuit For Configuring Memory<br>Core Integrated Circuit Dies With Memory<br>Interface Integrated Circuit Dies                              | US           |

| 0010       | US20099027702          | System And Method For Simulating A Different<br>Number Of Memory Circuits                                                                               | US           |

| 0011       | U5200800251 <b>37</b>  | System And Method For Simulating An Aspect Of A Memory Circuit                                                                                          | US           |

| 0312       | US20080025108          | System And Method For Delaying A Signal<br>Communicated From A System To At Least One<br>Of A Plurality Of Memory Circuits                              |              |

| 0013       | US20080025136          | System And Method For Storing At Least A Portion Of Information Received In Association With A First Operation For Use In Performing A Second Operation | US           |

| 0014       | U\$20080031072         | Power Saving System And Method For Use With<br>A Plurality Of Memory Circuits                                                                           | US           |

| 0015       | US20080025122          | Memory Refresh System And Method                                                                                                                        | US           |

| 0016       | US2XX80028135          | Multiple-Component Memory Interface System And Method                                                                                                   | US           |

| 0017       | 7379316                | Methods And Apparatus Of Stacking DRAMs                                                                                                                 | US           |

| 0018       | U520000028136          | Method And Apparatus For Refresh Management Of Memory Modules                                                                                           | US           |

| 0019       | US20080031030          | System And Method For Power Management In<br>Memory Systems                                                                                             | US           |

| 0020       | U\$2007005847 <b>1</b> | Methods And Apparatus of Stacking DRAMs                                                                                                                 |              |

| 0021       | PCT/US2007028109       | Methods And Apparatus of Stacking DRAMs                                                                                                                 | WO           |

| 0025       | 0520080027697          | Memory Circuit Simulation System And Method                                                                                                             | US           |

PATENT REEL: 026977 FRAME: 0906

| 0026 | US20080123459    | Combined Signal Delay And Power Saving                                                                                                              | US  |

|------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      |                  | System And Method For Use With A Plurality Of<br>Memory Circuits                                                                                    |     |

| 0027 | US20086027703    | Memory Circuit Simulation System And Method With Refresh Capabilities                                                                               | US  |

| 0028 | 60/823229        | Autonomous Refresh and Data Protection in<br>Memory Circuits                                                                                        | US  |

| 0030 | PC7452038063251  | Memory Circuit System and Method                                                                                                                    | WO  |

| 0034 | 60/826356        | System, Method And Computer Program Product For Multi-Rank Asymmetric Memory Modules                                                                | US  |

| 0035 | U520180007355    | Interface Circuit System And Method For<br>Performing Power Management Operations<br>During A Command Related Latency                               | S   |

|      | 7386.36          | Interface Circuit System And Method For<br>Performing Power Saving Operations In<br>Conjunction With Only A Portion Of A Memory<br>Circuit          | US  |

| 0038 | 7392338          | Interface Circuit System And Method For<br>Autonomously Performing Power Saving<br>Operations In Conjunction With A Plurality Of<br>Memory Circuits | US  |

| 0038 | US20080082763    | Apparatus And Method For Power Management Of Memory Circuits By A System Or Component Thereof                                                       |     |

| 0040 | 60/849631        | System And Method For Increasing Capacity And<br>Performance Of Flash Storage                                                                       | US  |

| 0041 | US20000086588    | System And Method For Increasing Capacity Performance, And Flexibility Of Flash Storage                                                             | US  |

| 0042 | 60/865624        | Memory Subsystem And Method                                                                                                                         | U5  |

| 44   | 60/865623        | Multi-Rank Partial Width Memory Modules                                                                                                             | US  |

| 0044 | 60/865627        | System And Method For Memory Control                                                                                                                | US  |

| 0046 |                  | System And Method For Adjusting The Timing Of<br>Signals Associated With A Memory System                                                            | US  |

| 0047 | US20080056014    | Memory Device With Emulated Characteristics                                                                                                         | US  |

| 0048 | US20070195613    | Memory Module With Memory Stack And<br>Interface With Enhanced Capabilities                                                                         | US. |

| 0049 | US20080126690    | Memory Module With Memory Stack                                                                                                                     | US  |

|      | US20070204075    | System And Method For Reducing Command<br>Scheduling Constraints Of Memory Circuits                                                                 | US  |

| 0052 | PCT/US2007095080 | Memory Circuit System And Method                                                                                                                    | wo  |

| 0053 | US20070192563    | System And Method For Translating An Address                                                                                                        | US  |

|      |                                | Associated With A Command Communicated Between A System And Memory Circuits                                                                          |          |

|------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0054 | US20080010435                  | Memory Systems And Memory Modules                                                                                                                    | US       |

| 0055 | US28080028137                  | Method And Apparatus For Refresh                                                                                                                     |          |

|      |                                | Management Of Memory Modules                                                                                                                         |          |

| 0056 | 11/855805                      | System, Method, And Apparatus For Allowing<br>Electrical Communication Between Integrated<br>Circuit Package Contacts And Circuit Board<br>Contacts  | VS       |

| 0060 | 12/144396                      | Memory Subsystem And Method                                                                                                                          |          |

| 0062 | US20080062773                  | System and Method for Simulating An Aspect Of<br>A Memory Circuit                                                                                    | US       |

| 0363 | 61/030534                      | Emulation Of Abstracted DIMMs Using<br>Abstracted DRAMs                                                                                              | US       |

|      |                                |                                                                                                                                                      | 110      |

| 9071 | 11/855826                      | System And Method For Providing Additional<br>Space Between An Integrated Circuit And A<br>Circuit Board For Positioning A Component<br>Therebetween | US       |

| 0073 | 11/939432                      | System For Multi-Pank Partial Width Memory<br>Modules                                                                                                | US       |

| 0074 | 11/858518                      | System And Method For Multi-Rank Asymmetric<br>Memory Modules                                                                                        | US       |

| 0075 | 11/941589                      | Optimal Channel Design For Memory Devices For Providing A High-Speed Memory Interface                                                                |          |

| 0076 | US20080120443                  | System And Method For Reducing Command<br>Scheduling Constraints Of Memory Circuits                                                                  | US       |

| 0077 | U520080109595                  | System And Method For Reducing Command                                                                                                               | US       |

|      |                                | Scheduling Constraints Of Memory Circuits                                                                                                            | ne.      |

| 0078 | US20080109206                  | Memory Device With Emulated Characteristics                                                                                                          | US       |

| 0079 | US20080126692<br>US20080126687 | Memory Device With Emulated Characteristics                                                                                                          | US       |

| 0800 | USZW80126688                   | Memory Device With Emulated Characteristics  Memory Device With Emulated Characteristics                                                             | U3<br>88 |

| 0082 | 1570080126689                  | Memory Device With Emplated Characteristics                                                                                                          | US       |

| 0083 |                                | Memory Device With Emulated Characteristics                                                                                                          | US<br>US |

| CO84 | US20080104314                  | Emulation Of Memory                                                                                                                                  | U5       |

| 0085 | US20080133825                  | System And Method For Simulating An Aspect                                                                                                           | 16       |

|      | CANTONICACION                  | Of A Memory Circuit                                                                                                                                  | N. W.    |

| 0086 | US20090024789                  | Memory Circuit System And Method                                                                                                                     | US       |

| 0087 | US20090024790                  | Memory Circuit System and Method                                                                                                                     | US       |

| 0088 | US20080109597                  | Method And Apparatus For Refresh<br>Management Of Memory Modules                                                                                     | US       |

| 0089 | US20080109598                  | Method And Apparatus For Refresh Management Of Memory Modules                                                                                        | US       |

-3.

| 0090 | 61/014740          | Embossed Heat Spreader                                                                                                                                  | US  |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0092 | DE12206001810      | An integrated Memory Core And Memory Interface Circuit                                                                                                  | DE  |

| 0093 | 2441726            | An Integrated Memory Core And Memory<br>Interface Circuit                                                                                               | GB  |

| 0094 | US2008544437       | An Integrated Memory Core And Memory Interface Circuit                                                                                                  | JP  |

| 0095 | 10-2008-7001812    | An Integrated Memory Core And Memory Interface Circuit                                                                                                  | KR  |

|      | 15.778.8172.998.77 | Interface Circuit System And Method For<br>Performing Power Management Operations in<br>Conjunction With Only A Portion Of A Memory<br>Circuit          | US  |

| 0099 | US20080239858      | Interface Circuit System And Method For<br>Autonomously Performing Power Management<br>Operations In Conjunction With A Plurality Of<br>Memory Circuits | US  |

| 0100 |                    | Memory Circuit System and Method                                                                                                                        | WC. |

| 0107 | 12/057306          | Standard Hybrid Memory Module                                                                                                                           | US  |

| 0108 | 12/378328          | Emulation Of Abstracted DIMMs Using Abstracted DRAM                                                                                                     |     |

| 0110 | US20080170425      | Methods And Apparatus of Stacking DRAMs                                                                                                                 | US  |

| 0111 | 01112006002300     | Methods And Apparatus of Stacking DRAMs                                                                                                                 | DE  |

| 0112 | G82444653A         | Methods And Apparatus of Stacking DRAMs                                                                                                                 | GB  |

| 0113 | 172009007024       | Methods And Apparatus of Stacking DRAMs                                                                                                                 | P   |

| 0114 | 10-2008-7005172    | Methods And Apparatus of Stacking DRAMs                                                                                                                 | KR  |

| 0115 | 12/203100          | Embossed Heat Spreader                                                                                                                                  | 115 |

| 0117 | 61/083497          | Memory Subsystem With Ganged Ranks                                                                                                                      | US  |

| 0120 | 2008-554369        | Memory Circuit System And Method                                                                                                                        | D   |

| 0121 | 10-2008-7019582    | Memory Circuit System And Method                                                                                                                        | KR  |

| 0122 | 70.50              | Memory Circuit System And Method                                                                                                                        | EU  |

| 0124 | 61/083878          | Memory Subsystem With Ganged Ranks                                                                                                                      | US  |

| 0126 | 12/503496          | Configurable Memory System                                                                                                                              | US  |

| 0127 | EU2054803          | Memory Circuit System And Method                                                                                                                        | EU  |

| 0130 | 51/185/85          | Programming Of DIMM Termination Resistance<br>Values                                                                                                    | 13  |

| 0133 | 12/507682          | System And Method For Simulating An Aspect<br>Of A Memory Circuit                                                                                       | US  |

|      |                    | Method And Circuit For Configuring Memory  Core Integrated Circuit Dies With Memory Interface Integrated Circuit Dies                                   | 15  |

FINAL-Patent Sale Agreement (6385602) DOC

----