# PATENT ASSIGNMENT COVER SHEET

Electronic Version v1.1 Stylesheet Version v1.2 EPAS ID: PAT5129745

| SUBMISSION TYPE:      | NEW ASSIGNMENT |

|-----------------------|----------------|

| NATURE OF CONVEYANCE: | ASSIGNMENT     |

### **CONVEYING PARTY DATA**

| Name           | Execution Date |

|----------------|----------------|

| UNIQUIFY, INC. | 04/17/2017     |

## **RECEIVING PARTY DATA**

| Name:           | UNIQUIFY IP COMPANY, LLC |  |

|-----------------|--------------------------|--|

| Street Address: | ONE MARKET, SPEAR TOWER  |  |

| City:           | SAN FRANCISCO            |  |

| State/Country:  | CALIFORNIA               |  |

| Postal Code:    | 94105                    |  |

## **PROPERTY NUMBERS Total: 21**

| Property Type       | Number   |

|---------------------|----------|

| Patent Number:      | 7975164  |

| Patent Number:      | 8843778  |

| Patent Number:      | 8990607  |

| Patent Number:      | 9021293  |

| Patent Number:      | 9081516  |

| Patent Number:      | 9075543  |

| Patent Number:      | 9552853  |

| Patent Number:      | 8947140  |

| Patent Number:      | 9100027  |

| Patent Number:      | 8941423  |

| Patent Number:      | 8941422  |

| Patent Number:      | 9300443  |

| Patent Number:      | 9584309  |

| Patent Number:      | 9425778  |

| Patent Number:      | 9898433  |

| Application Number: | 15853568 |

| Patent Number:      | 9431091  |

| Patent Number:      | 9805784  |

| Application Number: | 15722209 |

| Application Number: | 15996365 |

| -                   |          |

PATENT REEL: 046813 FRAME: 0080

505082987

| Property Type       | Number   |

|---------------------|----------|

| Application Number: | 16049693 |

#### **CORRESPONDENCE DATA**

Fax Number:

Correspondence will be sent to the e-mail address first; if that is unsuccessful, it will be sent using a fax number, if provided; if that is unsuccessful, it will be sent via US Mail.

**Phone:** 4089712573

Email: diana@zilkakotab.com

Correspondent Name: ZILKA-KOTAB, PC

Address Line 1: 1155 N. 1ST STREET, SUITE 105

Address Line 4: SAN JOSE, CALIFORNIA 95112

| NAME OF SUBMITTER: | KEVIN J. ZILKA |

|--------------------|----------------|

| SIGNATURE:         | /KEVIN ZILKA/  |

| DATE SIGNED:       | 09/07/2018     |

#### **Total Attachments: 12**

source=Uniquify Inc to Uniquify LLC#page1.tif source=Uniquify Inc to Uniquify LLC#page2.tif source=Uniquify Inc to Uniquify LLC#page3.tif source=Uniquify Inc to Uniquify LLC#page4.tif source=Uniquify Inc to Uniquify LLC#page5.tif source=Uniquify Inc to Uniquify LLC#page6.tif source=Uniquify Inc to Uniquify LLC#page7.tif source=Uniquify Inc to Uniquify LLC#page8.tif source=Uniquify Inc to Uniquify LLC#page9.tif source=Uniquify Inc to Uniquify LLC#page10.tif source=Uniquify Inc to Uniquify LLC#page11.tif source=Uniquify Inc to Uniquify LLC#page11.tif

#### ASSIGNMENT OF PATENT RIGHTS

**THIS ASSIGNMENT OF PATENT RIGHTS** (as amended, restated, amended and restated, supplemented or otherwise modified from time to time, this "**Assignment**") entered into as of April 17, 2017 (the "**Effective Date**"), between Uniquify IP Company, LLC, a Nevada limited liability company ("**Assignee**"), on the one hand, and Uniquify, Inc., a Delaware corporation ("**Parent**") and each Subsidiary of Parent identified in the signature pages hereto (together with Parent, collectively, "**Assignors**") on the other hand.

**SECTION 2. Assignment**. Each Assignor hereby sells, assigns, transfers, conveys, sets over, and delivers to Assignee all right, title, and interest, whether now or hereafter existing or existing, acquired or arising in, to, and under the following (collectively, the "**Assigned Patent Rights**"):

- (a) all patents owned or exclusively licensed to, issued to, or for which applications have been filed by or are pending in the name of, any Assignor, including, without limitation, the patents and patent applications set forth on **Schedule 1** attached hereto (the "**Assigned Patents**");

- (b) all patents and patent applications: (i) to which any of the Assigned Patents directly or indirectly claims priority; or (ii) for which any of the Assigned Patents directly or indirectly forms a basis for priority;

- (c) all reissues, reexaminations, extensions, renewals, continuations, continuations in part, continuing prosecution applications, requests for continuing examinations, and divisionals of any item in any of the foregoing categories (a) and (b);

- (d) all foreign patents, patent applications, and counterparts relating to any item in any of the foregoing categories (a) through (c), including, without limitation, certificates of invention, utility models, industrial design protection, design patent protection, and other governmental grants or issuances;

KE 46256387.11

- (e) all items in any of the foregoing in categories (b) through (d), whether or not expressly listed on the Schedule of Exceptions and whether or not claims in any of the foregoing have been rejected, withdrawn, cancelled, or the like;

- (f) inventions, invention disclosures, and discoveries described in any of the Assigned Patents or any item in the foregoing categories (b) through (e) that: (i) are included in any claim in the Assigned Patents or any item in the foregoing categories (b) through (e); (ii) are subject matter capable of being reduced to a patent claim in a reissue or reexamination proceeding brought on any of the Assigned Patents or any item in the foregoing categories (b) through (e); or (iii) could have been included as a claim in any of the Assigned Patents or any item in the foregoing categories (b) through (e);

- (g) all rights to apply in any or all countries of the world for patents or other governmental grants or issuances of any type related to any item in any of the foregoing categories (a) through (f), including, without limitation, under the Paris Convention for the Protection of Industrial Property, the International Patent Cooperation Treaty, or any other convention, treaty, agreement, or understanding;

- (h) all causes of action (whether known or unknown or whether currently pending, filed, or otherwise) and other enforcement rights under, or on account of, any of the Assigned Patents or any item in any of the foregoing categories (b) through (g), including, without limitation, all causes of action and other enforcement rights for (i) damages; (ii) injunctive relief; and (iii) any other remedies of any kind for past, current, and future infringement, misappropriation, or other violation; and

- (i) all rights to collect income, royalties, damages and other payments due or payable under or with respect to any of the Assigned Patents or any item in any of the foregoing categories (b) through (h).

For clarity, the "Assigned Patents" shall include all patents and patent applications assigned to Assignee, and that are deemed to be "Assigned Patents", pursuant to Section 7.18 of the Credit Agreement.

IN WITNESS WHEREOF, the parties have caused this Assignment to be executed by their duly authorized representatives as of the Effective Date.

#### ASSIGNEE:

UNIQUIFY IP COMPANY, LLC.

a Nevada limited liability company

By:

Name: Jung Ho (Josh) Lee Title: Chief Executive Officer

#### ATTESTATION OF SIGNATURE UNDER 28 U.S.C. § 1746

The undersigned witnessed the signature of JUNG HO (JOSH) LEE to the above Assignment of Patent Rights on behalf of UNIQUIFY IP COMPANY, LLC, a Nevada limited liability company and makes the following statements:

- I am over the age of 18 and competent to testify as to the facts in this Attestation block if called upon to do so.

- JUNG HO (JOSH) LEE is personally known to me (or proved to me on the basis of satisfactory evidence) and appeared before me on April \_\_\_\_\_\_\_, 2017 to execute the above Assignment of Patent Rights on behalf of UNIQUIFY IP COMPANY, LLC, a Nevada limited liability company.

- JUNG HO (JOSH) LEE subscribed to the above Assignment of Patent Rights on behalf of UNIQUIFY IP COMPANY, LLC, a Nevada limited liability company.

I declare under penalty of perjury under the Laws of the United States of America that the statements made in the three (3) numbered Sections immediately above are true and correct.

EXECUTED on April 12, 2017

Print Name:

[Signature Page to Assignment of Patent Rights]

#### ASSIGNOR:

UNIQUIFY, INC., a California corporation

Name: Jung Ho (Josh) Lee

Title: Chief Executive Officer

#### ATTESTATION OF SIGNATURE UNDER 28 U.S.C. § 1746

The undersigned witnessed the signature of JUNG HO (JOSH) LEE to the above Assignment of Patent Rights on behalf of UNIQUIFY, INC., a California corporation and makes the following statements:

- I am over the age of 18 and competent to testify as to the facts in this Attestation block if called upon to do so.

- JUNG HO (JOSH) LEE is personally known to me (or proved to me on the basis of satisfactory evidence) and appeared before me on April 12, 2017 to execute the above Assignment of Patent Rights on behalf of UNIQUIFY, INC., a California corporation.

- JUNG HO (JOSH) LEE subscribed to the above Assignment of Patent Rights on behalf of UNIQUIFY, INC., a California corporation.

I declare under penalty of perjury under the Laws of the United States of America that the statements made in the three (3) numbered Sections immediately above are true and correct.

EXECUTED on April /2, 2017

Print Name

(Signature Page to Assignment of Patent Rights)

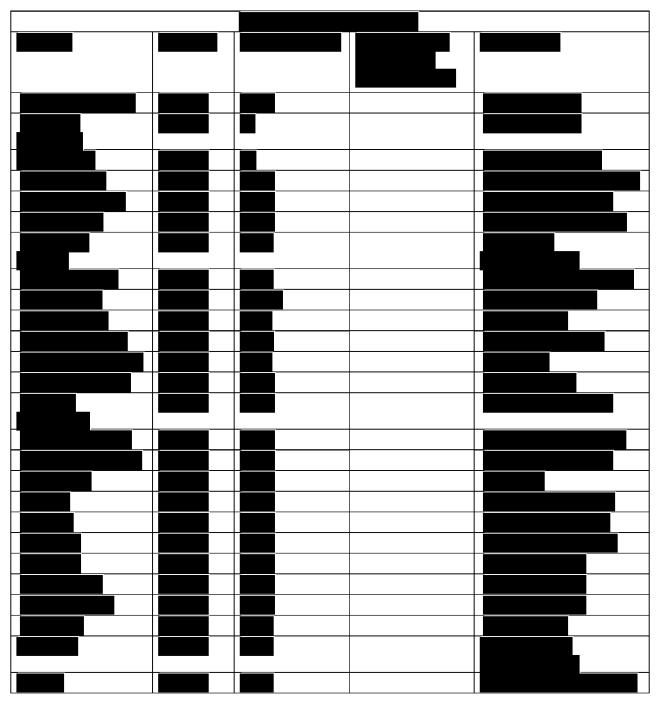

## Schedule 1

# **Assigned Patents**

| Inventor                                      | Patent or<br>Application<br>Number | Patent Date<br>or Filing<br>Date | Title (for Issued Patent)                                                                                                        |

|-----------------------------------------------|------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Lee; Jung, Gopalan;<br>Mahesh                 | 7,975,164                          | Jul.5, 2011                      | DDR memory controller                                                                                                            |

| Lee; Jung, Goplan;<br>Mahesh                  | 8,661,285                          | Feb. 25, 2014                    | Dynamically calibrated DDR memory controller                                                                                     |

| Lee; Jung, Goplan;<br>Mahesh                  | 8,843,778                          | Sep. 23,2014                     | Dynamically calibrated DDR memory controller                                                                                     |

| Iyer; Venkat, Joshi;<br>Prashant, Lee; Jung   | 8,941,422                          | Jan. 27, 2015                    | Method for operating a data interface circuit where a calibration controller controls both a mission path and a reference path   |

| Iyer; Venkat, Joshi;<br>Prashant, Lee; Jung   | 8,941,423                          | Jan. 27, 2015                    | Method for operating a circuit including a timing calibration function                                                           |

| Iyer; Venkat, Joshi;<br>Prashant, Lee; Jung   | 8,947,140                          | Feb. 3, 2015                     | Continuous adaptive training for data interface timing calibration                                                               |

| Lee; Jung, Gopalan;<br>Mahesh                 | 8,990,607                          | Mar. 24, 2015                    | Memory interface circuits including calibration for CAS latency compensation in a plurality of byte lanes                        |

| Gopalan; Mahesh                               | 9,300,443                          | Mar. 29, 2016                    | Methods for dynamically adaptive bit-leveling by incremental sampling, jitter detection, and exception handling                  |

| Lee; Jung, Goplan;<br>Mahesh                  | 9,021,293                          | Apr. 28, 2015                    | Methods for operating a memory interface circuit including calibration for CAS latency compensation in a plurality of byte lanes |

| Lee; Jung, Goplan;<br>Mahesh                  | 9,075,543                          | Jul. 7, 2015                     | Method of application memory preservation for dynamic calibration of memory interfaces                                           |

| Lee; Jung, Goplan;<br>Mahesh                  | 9,081,516                          | Jul. 14, 2015                    | Application memory preservation for dynamic calibration of memory interfaces                                                     |

| Iyer; Venkat, Joshi;<br>Prashant, Lee; Jung   | 9,100,027                          | Aug. 4, 2015                     | Data interface circuit for capturing received data bits including continuous calibration                                         |

| Lee; Jung, Iyer;<br>Venkak, Murdock;<br>Brett | 9,425,778                          | Aug. 23, 2016                    | Continuous Adaptive Data Capture Optimization for Interface Circuits                                                             |

[Schedule 1 to Assignment of Patent Rights]

| Gopalan; Mahesh,<br>Wu; David, Iyer;<br>Venkat | 9,431,091   | Aug. 30, 2016          | Multiple Gating Modes and Half-Frequency Dynamic<br>Calibration for DDR Memory Controllers                     |

|------------------------------------------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------|

| Lee; Jung, Goplan;<br>Mahesh                   | 9,552,853   | Jan. 24, 2017          | Methods for Calibrating a Read Data Path for a Memory Interface                                                |

| Gopalan; Mahesh                                | 9,584,309   | Feb. 28, 2017          | Circuit for Dynamically Adaptive Bit-leveling by Incremental sampling, Jitter Detection, and Exeption Handling |

| Lee; Jung, Iyer;<br>Venkat, Murdock;<br>Brett  | US15/237473 | Applied March 12, 2013 | Continuous adaptive data capture optimization for interface circuits                                           |

| Gopolan; Mahesh,<br>Wu; David, Iyer;<br>Venkat | US15/249188 | Applied June 6, 2008   | Multiple gating modes and half-frequency dynamic calibration for ddr memory controllers                        |

# Exhibit A

[Exhibit A to Assignment of Patent Rights]

KE 46256387.11

PATENT REEL: 046813 FRAME: 0093

**RECORDED: 09/07/2018**